| ■ HTBasic TOP ■ アイネット株式会社(i2net) HOME | ||||||||

|

| ■ GPIO(General Purpose Input/Output interface)とは... ■ ■ (チュートリアル) ■ |

|

GPIOインタフェースの由来 | GPIOインターフェースの概要 | 周辺装置の信号操作要求 データ・ハンドシェイク | GPIOタイム・アウト | GPIOインターラプト 多目的ライン | インターフェース・リセット | サマリー |

| GPIO(General Purpose Input/Output interface)/HPIOインタフェースの由来 | ||||||

| ||||||

| ||||||

|

■Topへ■ | ||||||

| GPIOインターフェースの概要 | ||||||

| ||||||

|

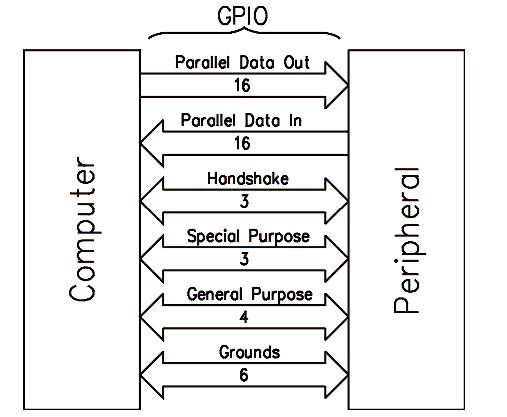

GPIOインターフェースは、50ピンコネクターを使用して周辺機器と情報のやり取りを行います。 32本のラインは、インプットとアウトプットのデータ用に使われます。 そのうち3本のラインが、ハンドシェイクに使われます。 また別の3本のラインは、特別の目的に使用されます。 その他の4本のラインは、多目的に利用されます。 グランド・ラインは6本、グランド・リファレンスのために提供されます。 2本は、定義されていないか、または接続されていません。

| ||||||

|

データラインには16本のデータ・アウトプットラインと16本のデータ・インプットラインがあります。これらのラインの判断ロジックを、ユーザが形成出来ます。 「DO UT Clear ジャンパー」は、リセットまたパワーアップの後で全てのアウトプット・データラインを「Low」にする事が出来る様にします。

| ||||||

|

3本のハンドシェークラインは、Peripheral Control line (PCTL)、Peripheral Flag line (PFLG)とInput/Output line (IO)です。 周辺装置の制御ラインは、データトランスファを始めるために、コンピュータによってセットされます。周辺装置は、トランスファ確認のために、Peripheral Flag lineを使います。これらの2本のラインは、ユーザが判断ロジックを形成できます。Input/Output lineは、周辺装置にデータの流れの方向を示します。信号レベル「high」は、周辺装置にアウトプットを行っていることを信号レベル「low」を示している間、周辺装置からのインプットを示します。

| ||||||

|

特別目的のラインはExternal Interrupt Request (EIR)、Peripheral Status (PST)、そしてPeripheral Status (PSTS)です。External Interrupt Requestラインは、周辺装置がコンピュータへの割り込みを可能にします。 Peripheral Statusラインは、周辺装置の現在の状況を得るために使用することができます。このラインの判断ロジックは、ユーザが形成できます。 コンピュータI/Oリセットが起こるときに、周辺装置をリセットするために最低でも15マイクロ秒、Peripheral Resetラインは「Low」となります。

| ||||||

|

多目的ラインは、コンピュータが設定できるCTL0 と CTL1の2本の制御ラインと、コンピュータが読み取ることのできるSTI0とSTI1というステータス・ラインがあります。

■Topへ■ | ||||||

| 周辺装置の信号操作要求 | ||||||

| ||||||

|

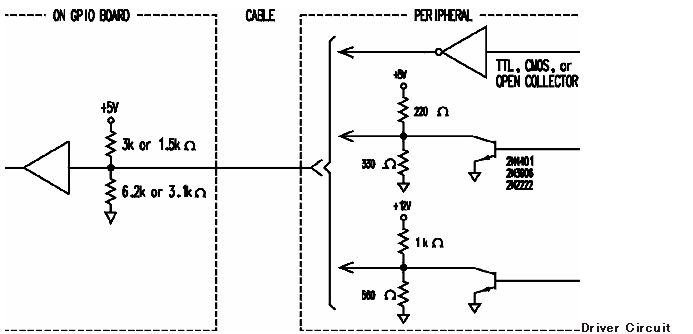

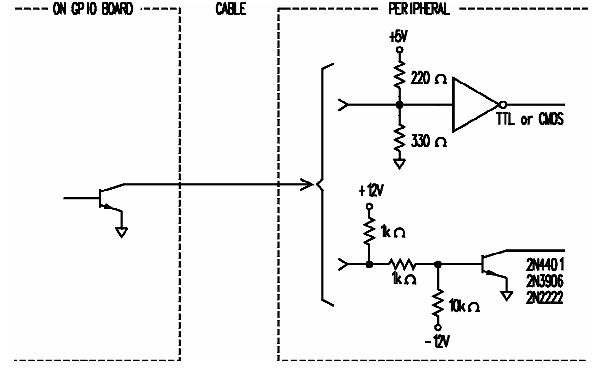

すべての信号とデータ・インプット・ラインは、TTL入力として接続されます。 データラインは、3K/6.2Kオームの抵抗で3.4Vにプルアップされます。 信号ラインは1.5K/3.1Kオームの抵抗で3.4Vにプルアップされます。 インプット電圧が5.5Vになると、GPIOインターフェースに対するダメージを与えることになります。

| ||||||

| ||||||

|

信号操作要求はデータ・ラインが2mA低く、信号ライン(PFLG, PSTS, STI0, STI1)が4.5mAです。最大電圧は、5.5Vです。 データ・ラインのハイ値は2.0Vより高く時でロ−値は0.7Vより低い時です。信号ラインでのロ−値は0.7Vより低い時です。

| ||||||

|

GPIOインターフェースのアウトプットは、全てオープン・コレクタ・ゲートで操作されます。 これは、ラインがハイ信号によって、自由に変わるか、あるいはロー信号で設置するかいずれかを意味します。 これは2つの結果を引き起こします。第1に、コンピュータは、周辺装置が必要とする30V以上の電圧に対し書くことが出来ます。 また第2には、ドライバは高い電圧まで引き上げねばならないか、周辺装置は低い値を読みます。

■Topへ■ | ||||||

| データ・ハンドシェイク | ||||||

|

データ・ハンドシェイクは、コンピュータと周辺装置の間でもう一方がデータを受けるかまたは送る用意ができているか知らせる信号を使用した方法です。

| ||||||

|

インターフェースのHNDスイッチはデータ転送を同期させる2つハンドシェーク・モード(フル・モードとパルス・モード)のうちの1つです。 もし周辺装置がハンドシェーク・データ転送にパルスを使用し、そしてタイミング要求を満たせば、パルス・モード・ハンドシェークが使用されるかもしれません。 もし周辺装置がパルス・モードのタイミング要求を満たさないときにはフル・モード・ハンドシェークを使用せねばなりません。

| ||||||

|

コンピュータは、現在のインプット・ラインからではなく、GPIOインターフェース上のデータ・バッファの中を読みこみます。 データがデータ・バッファへロードされた時に、データ-クロック・タイプとして選択されたスイッチは決まります。 RDYクロックは、PFLGのビジーからレディへの移り変わりでデータ・バッファをロードします。BSYクロックは、PFLGのレディからビジーへの移り変わりでデータ・バッファをロードします。 RDクロックは、バッファを読んでいる時にデータ・バッファをロードします。

| ||||||

|

もしSTATUSステートメントを使ってデータ・バッファを読めば、ライン・データが時間を計られるように、クロックが標準的RDにセットされるでしょう。 もしクロックがBSYまたはRDYであり、FPLGがトグルではないならば、STATUSステートメントはデータを決してロードしないという理由でインプット・ラインにかかわらず常に同じ値を返します。 | ||||||

|

完全なハンドシェイクは、5段階のステップをふみます。 | ||||||

|

ステップ1. コンピュータは、OUTPUTあるいはENTERステートメントのスタートの前にPSTラインを読み込むことによって周辺装置の状況チェックをします。 もしそれが論理値1なら、コンピュータは、転送を続けます。

| ||||||

|

ステップ2. コンピュータは、それぞれのデータ・ワードの転送を続ける前に、PFLGラインの状況を読み込むことによって周辺装置が使用可能かをチェックをします。 もしPFLGがレディ状態にあれば、コンピュータは実行を続けます。もしそうでないなら、コンピュータはPFLGがレディ状態から周辺装置が移るまで待ちます。 もしPFLGの状態を変えようとするならば、それは、フル・モード・ハンドシェークか、さもなければ、パルス・モード・ハンドシェークです。

| ||||||

|

ステップ3. コンピュータは、PCTLとIOのラインをセットすることによって転送を始めます。PCTLが転送のスタートを示す間、IOラインは、データ転送の方向を示します。

| ||||||

|

ステップ4. 周辺装置は、OUTPUTステートメントの間にデータ・ラインを読むか、あるいはINPUTステートメントの間にデータ・ライン上へデータを書かなくてはいけません。

| ||||||

|

ステップ5. 周辺装置は、PFLGラインをセットするかまたはクリアすることによってデータを読むかまたは書いたことを確認します。

| ||||||

|

GPIOインターフェースがコンピュータと周辺機器間でデータのハンドシェイクに多くのモードをサポートすることができるので、デバイスの検討では最もよい方法を決めることを要求されます。GPIOマニュアルは、9つのハンドシェイク方法のための詳細なタイミング・ダイアグラムを紹介しています。 ■Topへ■ | ||||||

| GPIOタイム・アウト | ||||||

|

タイム・アウトを使って周辺装置とのコミュニケーションがとれていない時、システムにロックがかかるのを妨げます。インターフェースが使用可能になるまで、PCTLラインがセットされ、状態が続くときに、タイム・アウト時限は始まります。 パルス・モードでの転送では、PCTLがクリアされるまで続きます。 フル・モードでの転送では、PCTLがクリアされPFLGがレディになるまで続きます。

| ||||||

|

タイム・アウトが起こるときに、インターフェースはリセットされます。 これは、セットしてからクリアしPRESETで、パルスはローになることです。 それからきれいにして前もって調節されている回線がそうであるPCTLが低く脈打つことを含みます。もしON TIMEOUTステートメントで、エラーをトラップで書けていなかった場合、プログラムはタイムアウト・エラーで終わります。

■Topへ■ | ||||||

| GPIOインターラプト(割り込み) | ||||||

|

GPIOインターフェースは、「Ready」「External Request」インタラプトをサポートします。 両方ともレベル・センシティブです(信号は、サービス可能になるまで残らなくてはいけません)。 リセットの後で、すべての割り込みは無効にされます。 期待する割り込みに対応するビットの一つを割り込み設定レジスタに書き込むことによって全ての割り込みは可能になります。

| ||||||

|

Interface Ready インターラプト インターフェース・レディがセットされるときに、割り込みはインターフェースが用意ができているようになればいつでも起こるでしょう。フル・モード・ハンドシェークでは、PCTLがクリアそしてPFLGがレディになればいつでも、インターフェースはレディとなります。 フル・モード・ハンドシェークでは、PFLGの状態にかかわらずPCTLがクリアされた時、インターフェースはレディとなります。 | ||||||

|

External Interrupt Request(外部割込み要求)

外部の割り込み要求(EIR)ビットがセットされた時、EIRラインがローになった時はいつでも、割り込みは起こるでしょう。 このラインの極性は、変えることができません。 このラインは、サブルーチンの中にあるか、プログラムによって回避されている間ローのままにしておかなくてはなりません。 ■Topへ■ | ||||||

| 多目的ライン | ||||||

|

自由に欲する使い方が出来る、4本の多目的ラインがあります。 CTL1とCTL0は、アウトプットラインでありSTI1とSTI2がインプット・ラインです。 ラインは、STATUS と CONTROLステートメントを通して読み込まれ、書き込まれます。

■Topへ■ | ||||||

| インターフェース・リセット | ||||||

|

インターフェース・リセットは、インターフェースを知られる状態にセットするために使用されます。 CLR I/O か RESET キーが押されたときに、パルスを発生します。 コントロールレジスター 0に1を書くことによってインタフェースはリセットされます。

■Topへ■ | ||||||

| サマリー | ||||||

|

GPIOインターフェースは、幅広いの周辺機器をインターフェース出来るフレキシブルな方法を提供します。 形成可能なデータ感知とハンドシェイク方法は、どんな周辺機器の使用もほとんど可能にします。

■Topへ■ | ||||||

| 【お 問 い 合 わ せ 先】 |

|

アイネット株式会社 E-mailでのお問い合わせ _/_/_/ Copyright 1998-2023 I2NET Co., Ltd. AllRights Reserved. _/_/_/ |